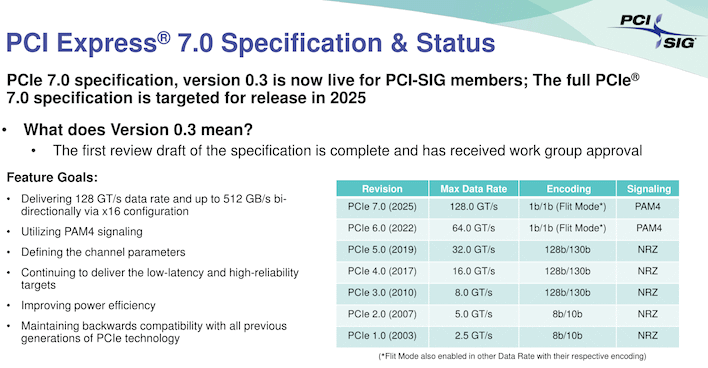

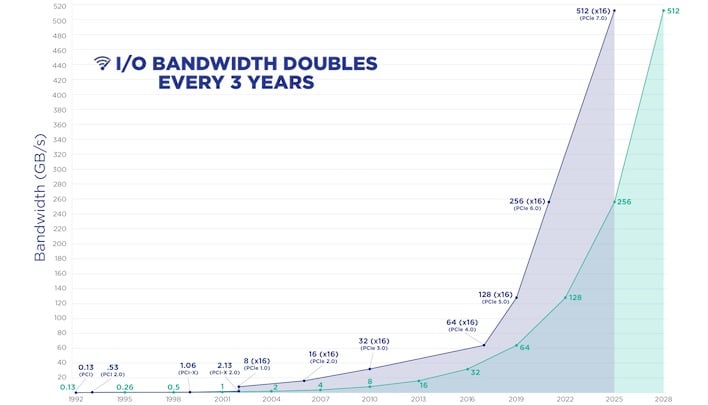

If you learn that and thought, “PCIe 7.0? What occurred to six.0?”, don’t be concerned—PCIe 6.0 is already finalized and nonetheless on monitor for product launches which can be probably coming subsequent yr or the yr after. It’s simply that PCI-SIG refuses to face nonetheless (as regular) and has now printed the primary draft specification for PCIe 7.0.

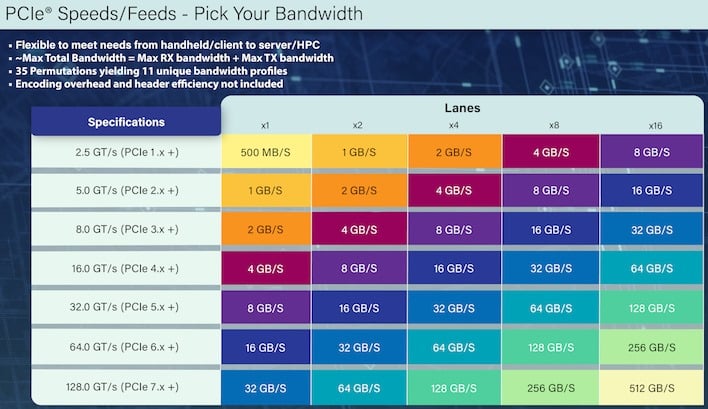

Of course, each are a lot sooner than the PCIe 4.0 and 5.0 connections out there in current-generation techniques, which run at 2GB/sec and 4GB/sec per path per lane, respectively. Even these switch charges are astonishing while you begin piling up the lanes; a typical PCIe 5.0 M.2 socket has some 16 gigabytes per second of full duplex bandwidth. An equal PCIe 7.0 gadget would theoretically help as much as 64GB/second transfers.

PCIe 7.0, in distinction, nonetheless makes use of PAM4 signaling, however now doubles the clock price as soon as once more. This goes to make some severe manufacturing challenges for firms constructing PCIe 7.0 {hardware}, as they should preserve extraordinarily clear signaling at ludicrously-high clock charges to make an excellent PCIe 7.0 connection.

You would possibly surprise why even trouble with such speeds presently. After all, the distinction between PCIe 4.0 and PCIe 5.0 for graphics playing cards is mainly nil, and even storage struggles to max out a PCIe 5.0 interface. That clearly will not be the case ceaselessly, however furthermore, there are already use-cases for sooner interconnects in massive servers and the high-performance computing area.

Besides extremely-high-speed networking and big storage arrays, there are additionally merchandise like Compute Express Link (CXL) that depend on the PCIe bodily layer to do their factor. CXL goals to be, amongst different issues, an interface for storage-class reminiscence, and reminiscence interfaces are often rather a lot sooner than current-gen PCIe.

The present publication is PCIe 7.0 draft model 0.3, and the specification is accessible to members of PCI-SIG. If you are of a thoughts to learn the specification, you will need to be a member, or get it type somebody who’s. For the remainder of us, nicely—PCI-SIG in all probability will not publish the ultimate PCIe 7.0 specification till 2025, and we probably will not see {hardware} with the interconnect till 2027 or later.