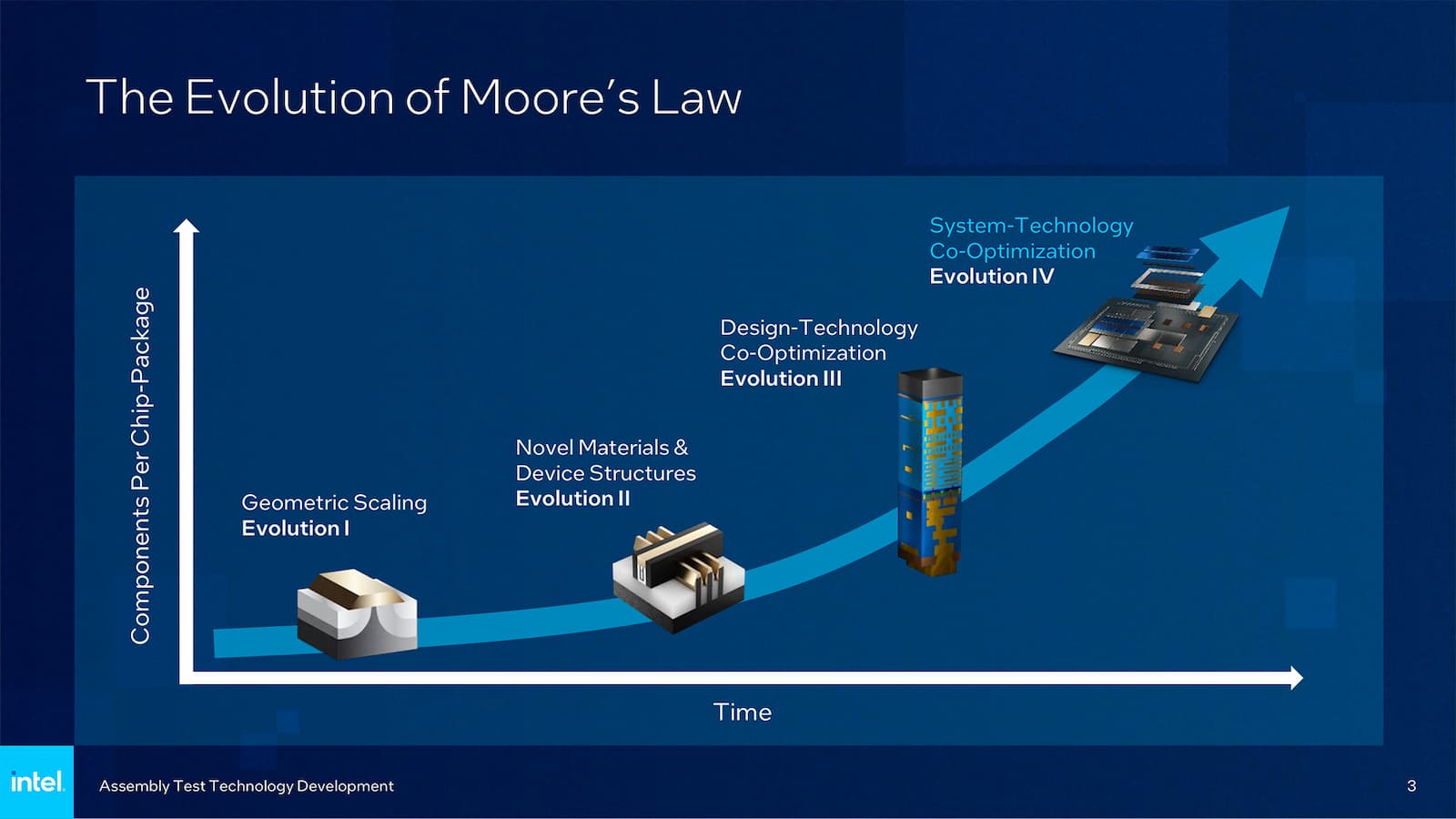

Once composed of a single piece of silicon, pc and server processors will more and more turn into compositions of logic blocks glued or stacked collectively. Focus on what will not be a development, however a prerequisite for the chip business’s continued race for efficiency.

The new Meteor Lake chip, which Intel has simply introduced intimately at its Innovation present, is in contrast to every other chip the American large has ever launched. This processor, which is able to begin showing in pocket book PCs on December 14 below the title Core Ultra , breaks with the corporate’s monolithic custom. You don’t want a microscope to see that the chip is a “collage” of a number of chip “items”. If we have been to make a wine analogy, the enormous Intel, which till now solely produced single-vineyard Burgundies, has transformed to mixing to turn into a Bordeaux producer!

We might be content material to say that the arrival of latest CEO Pat Gelsinger in 2021 was the start of many adjustments at Intel, which, with its IDM 2.0 technique, is making its revolution in a number of of its branches. This could be to miss the truth that AMD has been enjoying Lego for a while now, that Apple has already glued M1 Maxes collectively to make M1 Ultra. Or that many rumors level to Nvidia’s forthcoming conversion. So the query is much less why Intel has modified, however relatively what’s forcing high-power chip producers to design chips like units of bricks?

Foveros and Chiplets: optimizing prices to the max

The firstly purpose, as we talked about when the Meteor Lake chip was unveiled, is price. The indisputable fact that AMD and Intel now design their chips à la carte is firstly a manner of saving cash. Why etch the IO die in 4 nm if you can also make do with 7-8 nm? While the suitable engraving finesse is a vital issue, there’s additionally, and above all, an industrial logic behind it, based mostly on yields. And to know this logic, we have to delve into the fantastic world of semiconductor manufacturing. Semiconductors begin life on a wafer, that primordial wafer of silicon 300 mm in diameter and some microns thick.

After quite a few chemical baths coupled with a number of laser exposures to the scanners that print the circuits, the digital parts are reduce out and examined. Tested certainly, as a result of through the precise design of the chips, quite a few defects can seem on the floor of the wafer, typically rendering the affected components inoperable. Imagine a wafer with 10 errors scattered throughout its floor. If you narrow massive 3×4 cm chips, you find yourself with a really excessive waste price. Take the identical wafer and reduce 8×6 mm blocks, and your yield price explodes. This distinction in yield largely explains why the bigger the parts, the extra exponentially costly they turn into.

If assembling chips from items prices cash in addition to expertise (see beneath), then this mechanism can decrease the ultimate worth of a compound chip. In addition to this potential acquire in cash based mostly on pure yields, there’s additionally the flexibility to restrict the start-up prices of latest manufacturing nodes. Indeed, the manufacturing of a brand new element takes time to calibrate machines and processes, an costly start-up interval. Maximizing yields when introducing a brand new course of can considerably cut back start-up prices. Once the method has been mastered and peak yields achieved with small processors (or chips), it’s a lot simpler (and cheaper!) to use the identical recipe to bigger parts, which naturally have the next waste price.

We’ve been seeing this for years with smartphone chips: with their delirious volumes, greater margins and smaller chips, our smartphones profit from the thinnest etch nodes. The launch in early September of the iPhone 15 Pro and its 3 nm A17 Pro chip is a reminder of this – it’s the primary mass-produced chip on this etch finesse. And it’s good to see that the unimaginable manufacturing volumes of cell SoC gross sales are partially financing the pc chips of tomorrow!

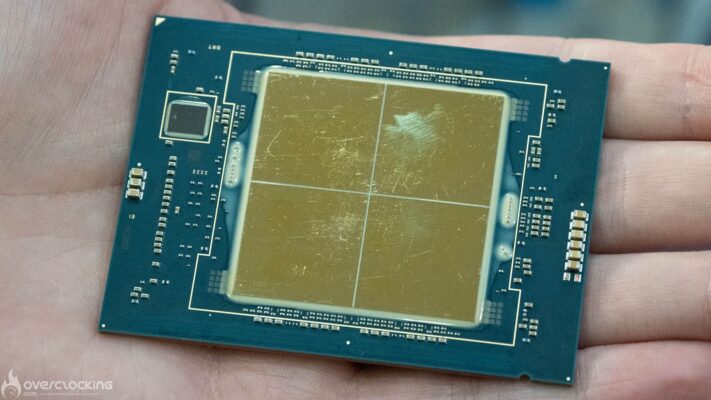

Please be aware that the period of chiplet meeting doesn’t imply the overall disappearance of enormous chips. Just have a look at the dimensions of the Cerebras mega-processor, which is actually the dimensions of a square-cut wafer (therefore the title wafer scale engine )! Some skilled chips corresponding to Xeon or EPIC, a few of that are already composed, nonetheless have relatively large chip items. This is to ensure most efficiency. Because disaggregated design brings with it limits and constraints, corresponding to better latency between sure chip parts, for instance. But these small losses may be partially restricted.

Facilitating diversification of the chip portfolio

Once yields had been accepted as the principle purpose for the “massive set of bricks”, the seek for price optimization linked to every designer’s portfolio of choices was added. Intel, AMD and others develop a whole lot of chip references yearly. Entry-level, mid-range or high-end chips, low-power or high-power chips: between buyer wants and vary results, processor distributors want selection.

In the traditional strategy to monolithic processors, one of many tips to creating totally different chips is to qualify them in a different way. Depending on the errors on the floor of the wafer, and the wants of selling segmentation, this implies reducing frequencies or deactivating a number of CPU or GPU cores – controlling the variety of lively cores within the numerous logic blocks is an efficient manner of influencing chip efficiency. This explains why the most cost effective Core i5 typically bodily resembles a Core i9. In the latter case, the chip has handed all of the assessments with flying colours and seems to be the final word model of the design. In the previous case, it’s a die that didn’t maintain up so nicely at excessive frequencies, and was lacking one or two cores.

Logic block meeting has one nice power right here: the flexibility for chip designers to create extremely complicated chips and/or a la carte. All with out having to undergo the method of qualifying a brand new monolithic chip design. What’s extra, they will reply exactly to a buyer who desires extra CPU cores, or a much less highly effective and cheaper built-in graphics unit.

Overcoming two-dimensional limits

Designing chip layouts is such a posh endeavor that AI is now wanted to search out the very best routing of data inside the circuits. Circuits which, it should be realized, are three-dimensional. This depth provides complexity, not solely through the design part, but in addition through the lithography (and testing!) phases. For instance, there’s a restrict to the variety of circuit layers that may be etched on the wafer floor, a restrict that forces us to unfold out. This will not be suitable with the necessity for compactness in our digital gadgets, whether or not smartphones or PCs.

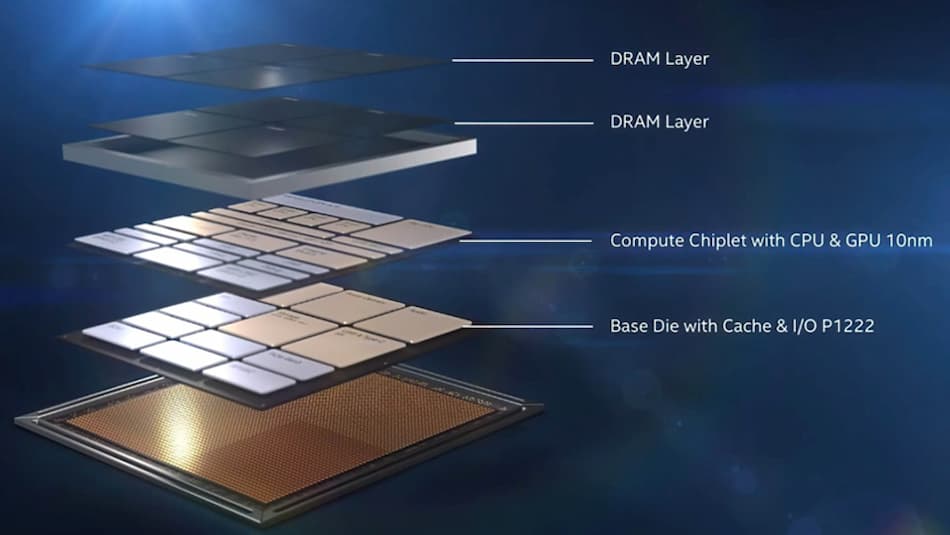

Here once more, the “massive block set” affords a brand new manner of getting round these limitations: stacking modules. All it’s important to do is go to your favourite on-line retailer to purchase such chips from AMD. Ryzen 9 7900X3D processors, labelled “X3D”, are traditional chips on which AMD (and TSMC!) have added cache reminiscence on the floor to facilitate the execution of sure duties (on this case, video video games). Why cache reminiscence? Because it’s made up of cells of a reminiscence known as SRAM, the restrict of which is that it doesn’t miniaturize in addition to the transistors within the logic blocks which might be the CPUs and GPUs. For a given floor space, engineers think twice about how a lot cache reminiscence they want, with every kilobyte consuming treasured floor space. Although there are limits, notably thermal – there’s an additional layer of warmth on prime of one other, which explains the considerably decrease frequencies of AMD processors designed on this manner – sticking reminiscence is a intelligent solution to profit from extra reminiscence at low price.

Note right here that AMD/TSMC aren’t the one ones who know the way to stack blocks: Intel was the primary with its Lakefield processor (2020), a really low-power chip that stacked 6 layers (together with substrate and reminiscence help), the final of which was nothing lower than RAM! At the Innovation Forum’s press Q&A session on September 18, Intel CEO Pat Gelsinger assured that cache stacking was not distinctive to AMD, and that Intel could be proposing comparable options utilizing its personal strategies.

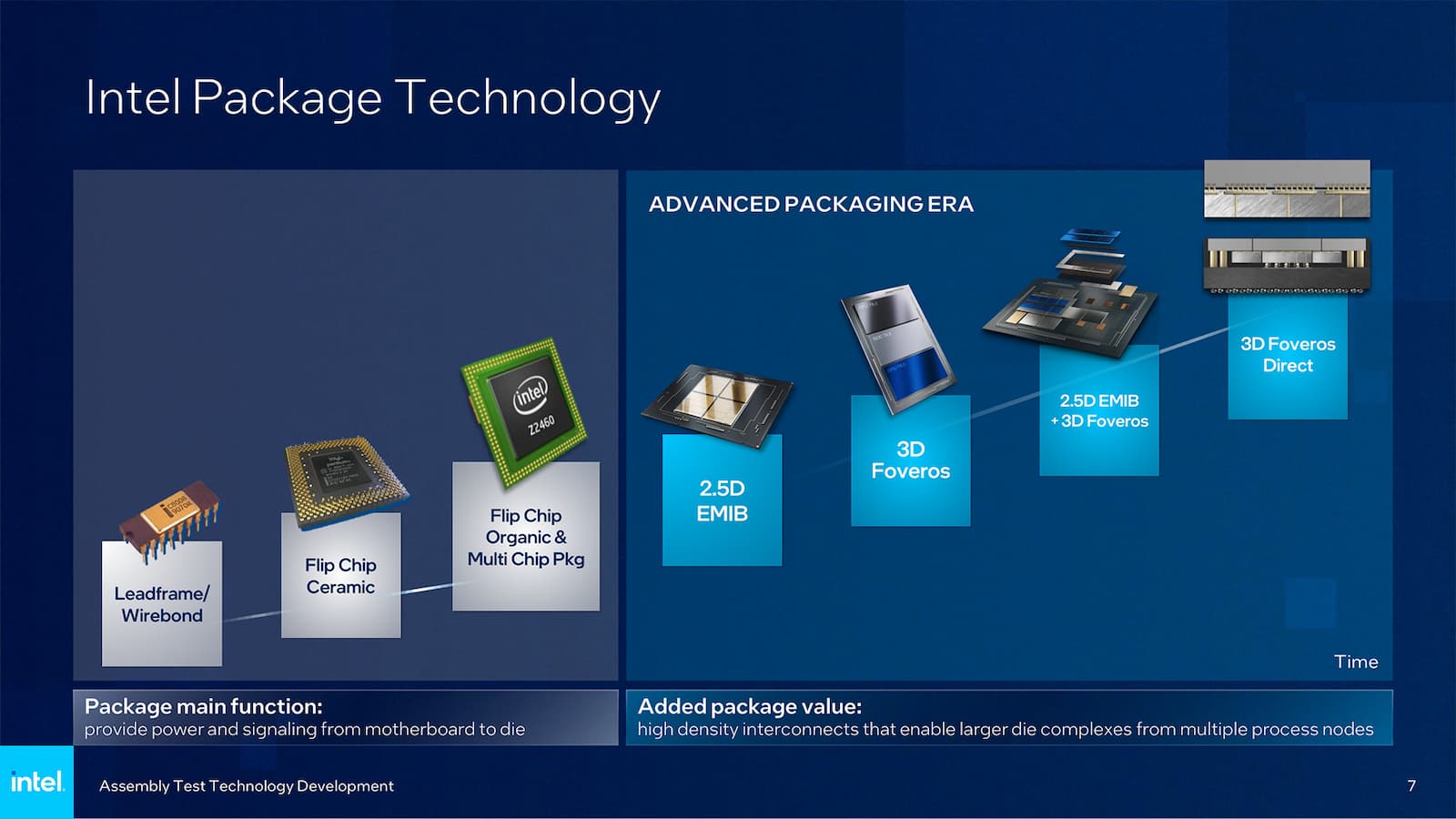

Assembly: Intel and TSMC prepared the ground

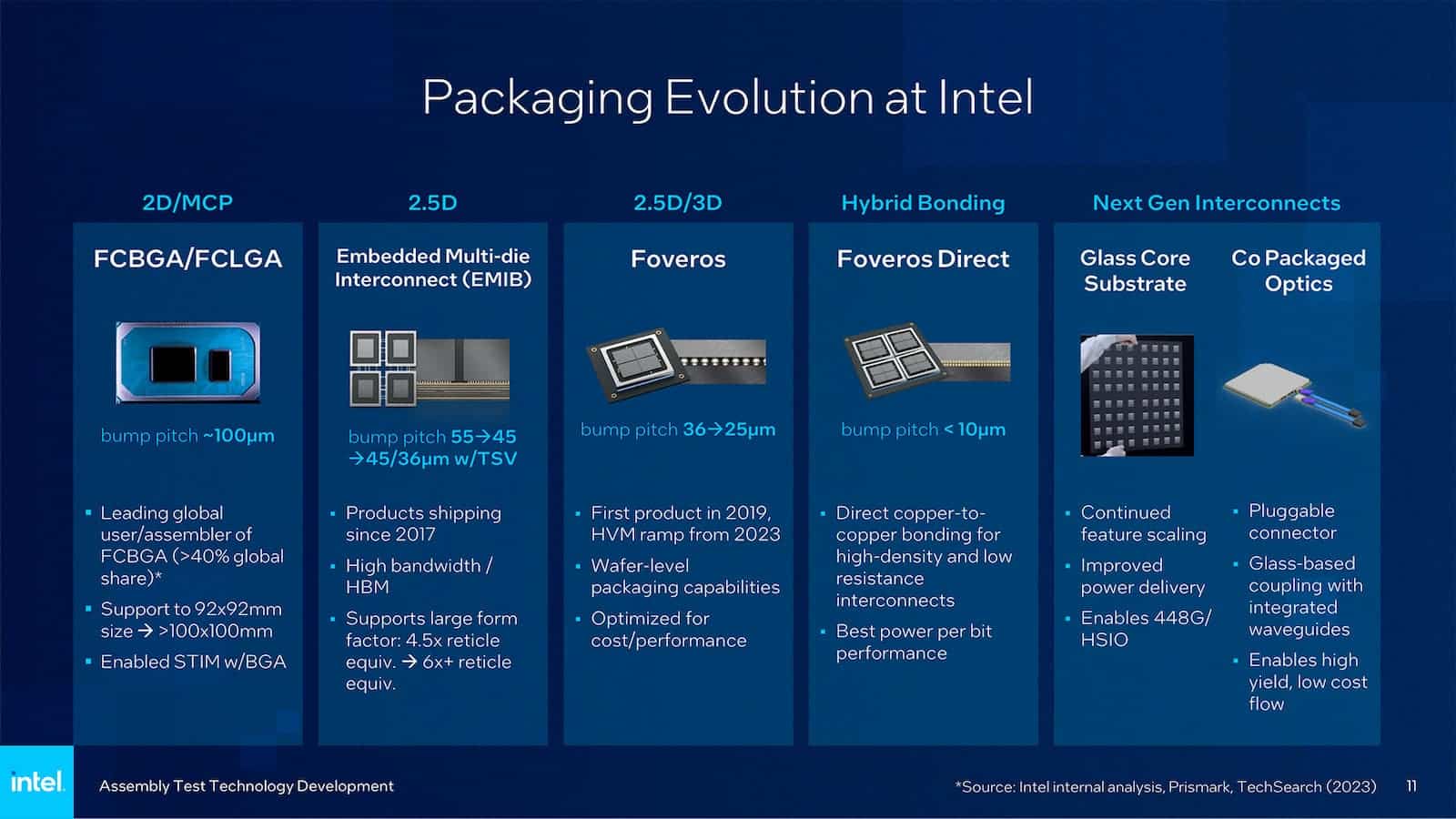

If you comply with semiconductor information, you’ve most likely heard of a few of these acronyms: EMIB, CO-EMIB and even Foveros at Intel or CoWoS at TSMC. These numerous “packaging” applied sciences, i.e. the mixing of die items with each other on a substrate, are the deadly weapons utilized by these two chip titans to push again the present limits of silicon. Whether we’re speaking in regards to the large EPYCs or the tiny Core Ultra, none of those merchandise would ever have seen the sunshine of day below these situations with out cutting-edge interconnection know-how all the way down to the micron.

Does this imply that these two corporations are the one ones who know the way to assemble or stack die items? Certainly not: along with the know-how of Samsung, STMicroelectronics, Sony (notably for stacked sensors) and Global Foundries, there are additionally gamers corresponding to Taiwanese ASE Technology Holdings, who specialize solely on this space of packaging (and testing). But Intel and TSMC are by far essentially the most superior, not solely by way of know-how and cutting-edge applied sciences, but in addition by way of manufacturing capability. This is a special kind of know-how from etching, which requires not solely further information, but in addition particular factories and machines. The two titans are thus battling it out for tens of billions of {dollars}. Intel alone has invested 7 and three.5 billion {dollars} between its Malaysian and Penang crops and its American plant in New Mexico (USA). And TSMC is doing the identical on its house turf, with the long run $2.9 billion Tongluo website, positioned in Miaoli County, within the north-west of the island.

Another benefit of block stacking is the potential of creating chips that have been as soon as inconceivable for yield causes, as we now have seen. As cooling strategies have improved – watercooling has turn into widespread in supercomputers – chip designers have been in a position to create monsters such because the “Datacenter GPU Max” graphics chip (codenamed Ponte Vecchio). But right here there’s one other restrict: the substrate.

This help for dies and chiplets – the “plate” on which blocks are glued, stacked and linked collectively – turns into a brand new frontier. And, as soon as once more, it’s Intel that might push again the present limits of the natural substrate on which producers place and join chip ends. Currently based mostly on laminated fiberglass, this heterogeneous materials can’t be used to compose the enormous chips the business wants. And the density of the holes – which permit interconnection circuits to cross between the totally different chip “items” – is restricted. That’s why Intel has been working for years on a brand new homogeneous glass substrate, which ought to see the sunshine of day in industrial functions by the top of the last decade. A substrate that can allow Intel to stack extra bricks – greater and greater bricks at that.

While the discount in circuit finesse will turn into more and more constraining as we strategy bodily limits, the meeting sport that producers at the moment are enjoying, with the promise of large chips that it brings with it, guarantees to maintain Moore’s well-known legislation alive for just a few extra years. And fulfill mankind’s unquenchable thirst for computing energy.