Microprocessors are essentially the most advanced issues people have ever constructed. In any advanced system, radically altering one a part of a system all the time has knock-on results for different elements of the system. To fight this, you’ll be able to attempt to de-couple interconnected elements of the system, and that is been a well-liked thought in semiconductors these days. Just take a look at the rise of chiplet or “disaggregated” processors.

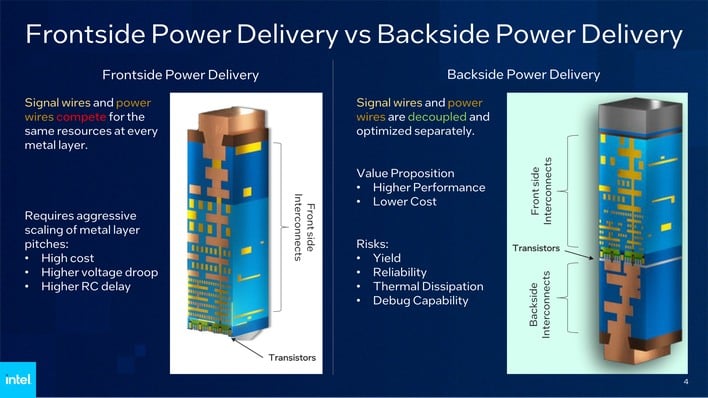

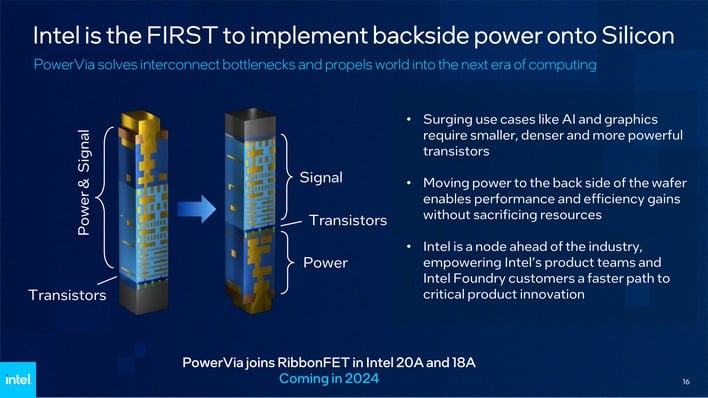

Well, if we apply this similar thought at a decrease stage, there’s an apparent goal for decoupling: the sign and energy wires contained in the microprocessor itself. As Intel explains it, processors are historically created like constructing a pizza, stacking on layers that aggressively scale in pitch, or measurement. This signifies that signalling and energy supply should compete for sources (like space and thermal limits) at each steel layer throughout the chip.

Moving the facility supply circuitry to the again aspect of the chip simplifies issues lots, and it provides improved efficiency in addition to decreased manufacturing value, however there are many points this strategy, too. After all, it isn’t a totally novel thought—Intel’s personal work on the idea started over a decade in the past. The factor is, we have reached some extent in transistor scaling the place the beneficial properties from a “Back Side Power Delivery Network” (BS-PDN) are too nice to disregard.

As Intel’s slide admits, the most important dangers related to bottom energy supply are worse yields, decreased reliability, hampered thermal dissipation, and crippled debug functionality. Naturally, Intel says that it has overcome these challenges in its first working implementation of BS-PDN, often called PowerThrough.

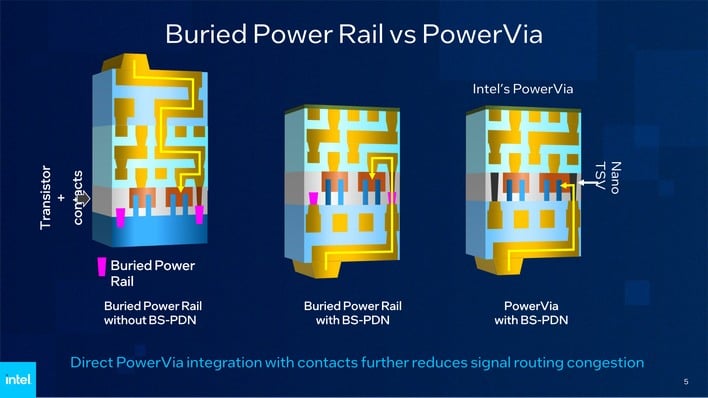

So, what’s so intelligent about PowerThrough in comparison with earlier bottom energy supply ideas? It’s using a factor that Intel calls “Nano TSV”. TSV after all stands for “through-silicon by way of” and try to be conversant in the time period by now, because it’s the best way that stacked chips (like AMD’s 3D V-Cache) are related. Nano-TSVs are, in accordance with Intel, five-hundred instances smaller than typical TSVs.

These are used to ship energy straight to the M0 layer the place the processing truly occurs quite than having to go by way of the M0 layer. This enormously simplifies issues, and it permits Intel some respiratory room on that layer because it would not should account for further energy routing mucking up the signaling above the M0 layer.

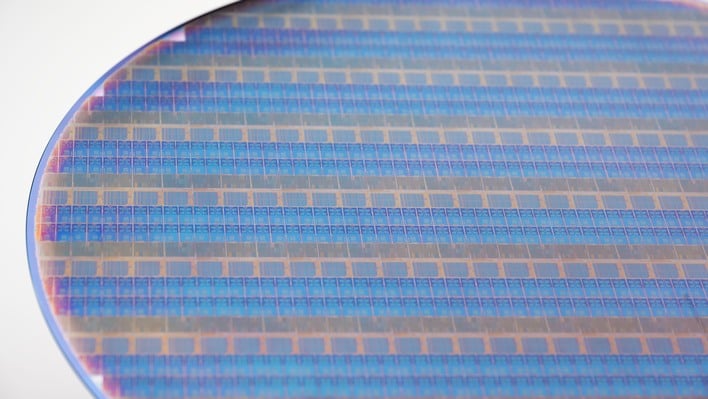

The massive announcement at the moment is that Intel has PowerThrough working proper now in check chips created utilizing a modified model of its Intel 4 course of. Intel 4 is already on the mass manufacturing stage, with good yields, and the boys in blue need to convey this tech to bear in opposition to its rivals on the next-gen 20A course of. With that in thoughts, a modified Intel 4 course of serves as the right testbed for the brand new tech.

These check chips are often called “Blue Sky Creek” and are easy processors with only a pair of Crestmont E-core clusters. Intel did not discuss concerning the efficiency or capabilities of Blue Sky Creek; it is unlikely that these chips will ever discover their approach into any manufacturing system. The level is that these chips are fabricated utilizing Nano TSVs related to BS-PDN and that all of it works as anticipated.

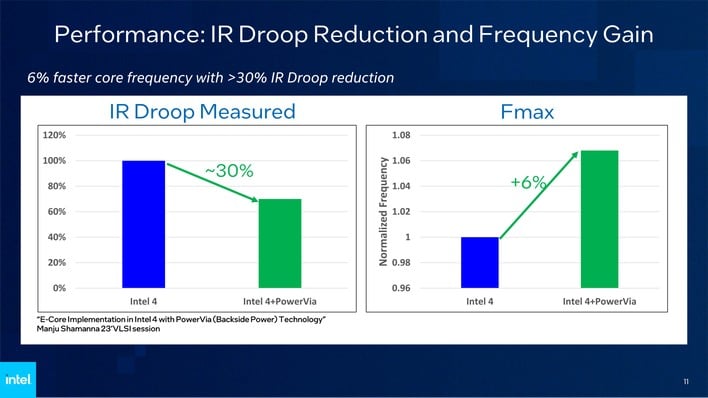

However, Intel did present some numbers for us to salivate over: a 30% discount in voltage droop signifies that chips can use decrease voltage to start with, bettering effectivity and lowering energy consumption. This comes together with a 6% improve within the most achievable core frequency, which sounds small, however is not unhealthy in any respect contemplating we’re essentially speaking about the identical Intel 4 manufacturing course of. Increasing clocks by 6% with decrease energy and no die shrink is fairly good.

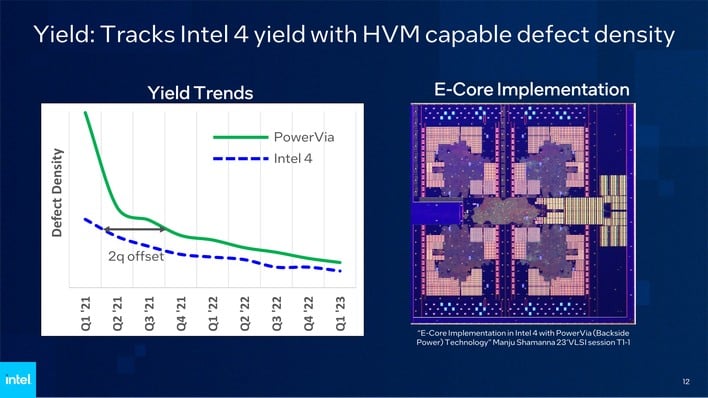

As far as yields go, properly, they’re worse—however Intel says that yields on this modified Intel 4 course of have been monitoring behind yields on the usual Intel 4 course of by about two quarters. In different phrases, the defect fee is trending down, which signifies that Intel’s foundry is determining the best way to make these chips with fewer defects. According to the chart in Intel’s slide, it appears to be like just like the defect fee now could be solely barely worse than on the usual Intel 4 course of.

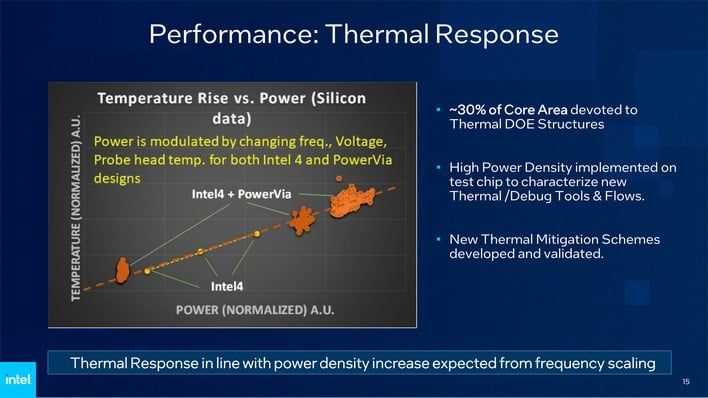

Finally, so far as thermals go, Intel has taken vital measures to take care of the truth that there’s now silicon between the transistors and the heatspreader or cooling equipment. The slide above says that thermal response is “in step with energy density improve anticipated from frequency scaling.” In different phrases, it says that thermal response of those chips is not truly worse than that of ordinary Intel 4 processors.

That does look like primarily right down to Intel’s measures to stop thermal response from being horrible, and people measures, if we’re understanding Intel’s slide accurately, embody some 30% of the core space being dedicated to buildings meant to enhance thermal switch.

In any occasion, Intel is rightfully stoked concerning the manufacturing success, and says that PowerThrough will probably be used on RibbonFET processors manufactured on the corporate’s 20A and 18A course of nodes. As deliberate, these chips will apparently begin displaying up subsequent 12 months. If it succeeds, Intel will probably be forward of the sport for certain, as neither TSMC nor Samsung are anticipated to have bottom energy supply prepared earlier than 2026.